半導体業界で注目を集めるチップレット技術。微細化の限界に直面する中、この革新的なアプローチが半導体の性能向上と製造コスト削減の鍵となっています。本記事では、チップレット技術の最新動向から市場規模、技術的課題まで、包括的に解説します。

チップレット関連の最新ニュース

- UCIe 2.0規格の登場

Universal Chiplet Interconnect Express(UCIe)コンソーシアムが2024年8月に「UCIe 2.0」仕様をリリースしました。新規格では3Dパッケージングがサポートされ、チップレットの帯域幅密度と電力効率が大幅に向上しています。

- チップレット集積プラットフォーム・コンソーシアム設立

2022年10月1日、東京工業大学、大阪大学産業科学研究所、東北大学を中心に、32社の企業が参加するチップレット集積プラットフォーム・コンソーシアムが設立されました。三次元集積技術、光集積技術などを含む、チップレット集積プラットフォーム技術全般の研究開発を目指しています。東京工業大学の研究チームが”Pillar-Suspended Bridge (PSB)”と呼ぶ新しいチップレット集積技術を開発しました。この技術は、広帯域のチップ間接続性能とチップレット集積規模の拡大を最小限の構成と製造プロセスで実現するものです。

チップレットとは?

チップレットの定義

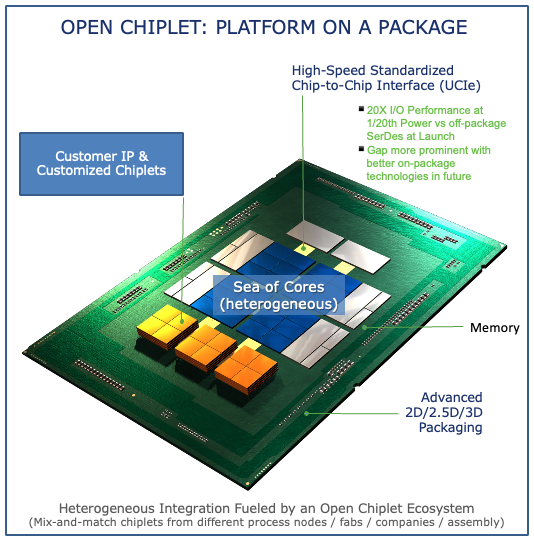

チップレットとは、従来の1つの大規模なチップに集積されていた回路を、複数の小さなチップに分割し、それらを組み合わせて1つの大きなチップのように機能させる技術です。

↑画像引用元:UCle

チップレット技術の利点

チップレット技術の主な利点は、歩留まりの向上、コスト削減、設計の自由度向上です。小さな面積で製造されるため、製造欠陥の影響が小さく、ウェハーの歩留まりが向上します。また、最先端プロセスを一部分にのみ使用することでコストを抑えられ、機能ごとに最適なチップレットを組み合わせられるため、柔軟な設計が可能になります。

チップレット技術の背景

半導体の微細化が限界に達しつつある中、チップレット技術は「ムーアの法則」を超えた「モア・ザン・ムーア(More than Moore)」の動きの一環として注目されています。3次元的なチップ間の接続を実現するため、FO-WLP、3D-IC、2.5Dシリコンインターポーザなどのプロセスが開発されてきました。

チップレット標準化に向けた取り組み

UCIe(Universal Chiplet Interconnect Express)

UCIeは、半導体およびパッケージング企業、ファウンドリー、クラウドサービスおよびIPサプライヤーなど、80社を超える企業のコンソーシアムによって2022年3月に発表された、ダイツーダイ接続のオープンな業界標準規格です。UCIe 2.0では、3Dパッケージングのサポートや、チップレットのSiP(System in Package)ライフサイクルにわたるテスト、管理、デバッグを考慮した設計(DFx)の課題に対応しています。

Alibaba、AMD、Arm、ASE、Google Cloud、Intel、Meta、Microsoft、NVIDIA、Qualcomm、Samsung、TSMC

BoW(Bunch of Wires)インターコネクト技術

BoWは、単一パッケージ内の1対のダイ間(D2D)のオープンで相互運用可能な物理インタフェースを定義しています。SoCの分割に最適化された物理層(PHY)を規定して、チップレットのマルチダイ相互接続の基盤を形成しています。

HBM(High Bandwidth Memory)

HBMは、シリコン貫通ビア(TSV)を使用して、さまざまな層のメモリチップを相互に積み重ねる技術です。当初はメモリとプロセッサ間のデータ移動距離を短縮するために設計されましたが、現在ではチップレット設計に欠かせない要素となっています。

チップレットの市場規模

急成長するチップレット市場

チップレット市場は急速に拡大しており、その成長率は目覚ましいものがあります。市場調査会社Market.USによると、世界のチップレット市場規模は2023年の31億ドル(約5000億円)から、2024年には44億ドル(約7000億円)に拡大すると予測されています。

2033年の市場予測

同じ調査によると、2033年にはチップレット市場が1070億ドル(約17兆円)にまで成長すると予測されています。この急激な成長は、AI、車載電子機器、消費者向け電子機器、データセンターなどの産業の発展に伴う高性能コンピューティングの需要増加によるものです。

年平均成長率(CAGR)

チップレット市場の年平均成長率(CAGR)は、2023年から2033年にかけて42%以上と予測されています。この驚異的な成長率は、チップレット技術が半導体産業に革命をもたらす可能性を示唆しています。

チップレットの主な用途

人工知能(AI)とデータセンター

チップレットは、AIプロセッサの性能向上と電力効率化に大きく貢献しています。異なる機能を持つ専用コアを1つのパッケージに統合することで、推論やトレーニングなどの複雑なAIタスクを効率的に処理できます。データセンターでは、高性能コンピューティングの需要に応えるため、チップレット技術が積極的に採用されています。

自動車産業

自動車業界では、高度な運転支援システム(ADAS)や自動運転技術の発展に伴い、高性能かつ省電力な半導体デバイスの需要が高まっています。チップレット技術を用いることで、複雑な処理を行う車載コンピュータの性能向上と小型化が可能になります。業界専門家の予測によると、自動車向けチップレットの本格的な採用は2027年から2030年の間に始まると見られています。

消費者向け電子機器

スマートフォン、タブレット、ウェアラブルデバイスなどの消費者向け電子機器でも、チップレット技術の採用が進んでいます。例えば、AMDのRyzen 7 5800X3Dデスクトップ CPUでは、チップレット技術により15%のゲーミング性能向上を実現しています。今後は、AI処理、グラフィックス、電力管理など、特定の機能に最適化されたコンポーネントを組み合わせることで、さらなる性能向上と省電力化が期待されています。

チップレットの主な種類

プロセッサチップレット

プロセッサチップレットは、中央演算処理装置(CPU)や画像処理装置(GPU)の機能を担う小型チップです。例えば、AMDのEPYCサーバー用プロセッサでは、複数の8コアCPUチップレットを組み合わせて高性能なマルチコアプロセッサを実現しています。これにより、製造コストの削減と性能の柔軟なスケーリングが可能になっています。

メモリチップレット

メモリチップレットは、高帯域幅メモリ(HBM)やキャッシュメモリなどの機能を提供します。例えば、HBMチップレットは、シリコン貫通ビア(TSV)技術を用いて複数のDRAMチップを垂直に積層することで、高速かつ大容量のメモリを実現しています。これにより、AIやビッグデータ処理などの高性能コンピューティング分野で必要とされる大量のデータ転送を効率的に行うことができます。

I/Oチップレット

I/O(入出力)チップレットは、外部デバイスとの通信や信号処理を担当します。例えば、AMDのEPYCプロセッサでは、Server IO DieやClient IO Dieと呼ばれるI/Oチップレットが使用されています。これらのチップレットは、CPUコアよりも緩いプロセスで製造されることで、コスト削減と周辺回路との互換性確保を両立しています。I/Oチップレットの採用により、システム全体の柔軟性と拡張性が向上します。

チップレットの技術的な課題

シグナルインテグリティの確保

チップレットは通常、短距離で信号を駆動するように設計されているため、その入出力(I/O)は電力効率を考慮して最適化されており、出力が比較的弱くなっています。チップレットをプローブする際、出力はテスターにラインを駆動する必要があり、これはバッファーの能力を超える要求となる場合があります。この制限により、テスト時間が大幅に遅くなり、高速でのテストが困難になる可能性があります。

複雑な相互接続の管理

多くのチップレットはプロトコルトランスレータとして機能し、最終パッケージ製品が複数のインターフェイスと通信できるようにしています。これらの複雑なプロトコルは、ダイレベルで徹底的に検証する必要があります。このため、信号損失のある環境での高速テストが必要となり、テストの複雑さが増大します。また、チップレット間の相互接続の設計と最適化も重要な課題となっています。

熱管理と電力効率

チップレットを高密度に集積すると、熱の問題が顕著になります。特に3D積層構造では、内部のチップレットの冷却が困難になる可能性があります。また、チップレット間の通信に必要な電力も無視できません。UCIe 2.0規格では、電力と熱の管理メカニズムが導入されていますが、これらの課題に対する効果的な解決策の開発は、チップレット技術の更なる普及に向けて重要です。

チップレットのトップシェアメーカー

Intel Corporation(米国)

Intelは、チップレット技術の先駆者の一つです。同社のFoveros技術は、3D積層チップレットを実現し、高性能と省電力を両立しています。また、EMIBと呼ばれる2.5D技術も開発しており、チップレット間の高速接続を可能にしています。Intelは、UCIeコンソーシアムの主要メンバーとしても、チップレット技術の標準化に貢献しています。

Advanced Micro Devices, Inc.(AMD、米国)

AMDは、EPYCサーバープロセッサやRyzenデスクトッププロセッサにチップレット技術を積極的に採用しています。同社のInfinity Fabric技術は、複数のCPUダイを効率的に接続し、高性能なマルチコアプロセッサを実現しています。AMDのチップレット採用により、サーバーおよびデスクトップ市場でのシェア拡大に成功しています。

TSMC(台湾積体電路製造、台湾)

TSMCは、世界最大の半導体ファウンドリーとして、多くのチップレット関連技術を開発しています。同社のCoWoS(Chip on Wafer on Substrate)やInFO(Integrated Fan-Out)技術は、高性能チップレットの製造と集積を可能にしています。TSMCは、多くの半導体設計企業にチップレット製造サービスを提供しており、業界全体のチップレット技術の発展に大きく貢献しています。

まとめ

チップレット技術は、半導体産業に革命をもたらす可能性を秘めています。微細化の限界を超えて、性能向上とコスト削減を実現する新たなアプローチとして、急速に普及が進んでいます。UCIeなどの標準化の取り組みにより、異なるベンダー間でのチップレットの相互運用性が向上し、さらなる技能向上と革新が期待されます。

一方で、シグナルインテグリティの確保や複雑な相互接続の管理、熱管理と電力効率の最適化など、技術的な課題も残されています。これらの課題を克服することで、チップレット技術はAI、自動車、データセンター、消費者向け電子機器など、幅広い分野でさらなる進化を遂げるでしょう。

チップレット市場は今後10年で急速に拡大し、2033年には約17兆円規模に達すると予測されています。Intel、AMD、TSMCをはじめとする主要企業の技術開発競争が激化する中、日本の産学連携による研究開発も活発化しています。

チップレット技術は、半導体業界の未来を形作る重要な要素となっており、今後の動向に注目が集まっています。

参考サイト

- UCIe公式ウェブサイト

- チップレット集積プラットフォーム・コンソーシアム

- AMD公式ウェブサイト

- Intel公式ウェブサイト

- TSMC公式ウェブサイト

- Market.US調査レポート

- 東京工業大学ニュースリリース

- Semiconductor Engineering

- EE Times

- IEEE Spectrum

- チップレット時代の到来〜半導体製造プロセスの中間工程で新市場を創出!

- チップレットのニュース一覧 ニュースイッチ by 日刊工業新聞社

- Will 2025 Be the Year of the Chiplet?

- チップレットとは?:複数の小規模回路への分割⇒統合戦略💡|半導体Times

- What is a Chiplet?

- 注目が集まるチップレット技術に重要な3つの規格

- チップレットの世界市場規模調査&予測、プロセッサ別パッケージング技術別最終用途別地域別分析、2023-2030年

- 『半導体業界の第一人者,AI業界を行く!』 Vol.11:半導体の新潮流 -チップレット- HACARUS INC.

- 半導体チップレットテストにおける複雑な課題への取り組み

- 半導体チップレット技術で注目の3銘柄、日本にもあるの?

- Chiplet Market by Type, Product, End User, and Region – Global Forecast to 2028

- 大阪大学大学院工学研究科 チップレット集積技術に関する共同研究講座を設置

- チップレットの標準化、UCIeが主導権を握る